Designing FPGA or SoC circuits with power constraints #FPGA @HacksterIO

Via Adam Taylor om Hackster.io – we all like to think we’re good at making circuits but rarely do we put in the extra work to figure out how to best power a project, especially in restrictive power or thermal environments. Adam writes:

Several of the projects I am working on at the moment are required to work with power constrained supplies.

There are a number of reasons why the design is power constrained — from being expected to operate via a battery for a long period of time to operating in a environment where the thermal dissipation is tightly controlled.

Design tips listed include:

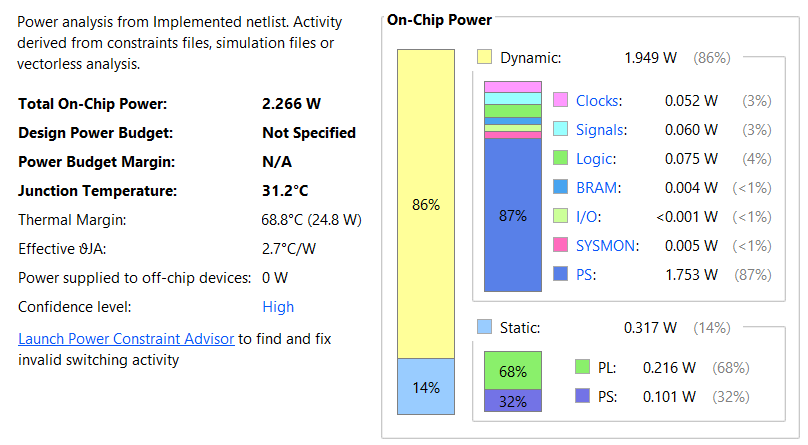

- Create a power budget

- Select the smallest device in the largest package available

- Firm up on the IP blocks used, new IP to be created, pin out, clocking and reset strategy, etc.

- Carefully consider the IO standard and configuration used

See the entire article on Hackster.io to see the analysis and tips for power in an FPGA design.